# LDO Regulator, 150 mA, 38 V, Low Noise, ADJ/FIX, with PG

# Product Preview **NCP731**

The NCP731 device is based on unique combination of features – very low noise, low quiescent current, fast transient response and high input and output voltage ranges. The NCP731 is CMOS LDO regulator designed for up to 38 V input voltage and 150 mA output current. Very low noise (10 µV<sub>RMS</sub>) makes this device an ideal solution for application where clean voltage rails are critical for system performance (power operational amplifiers, analog-to-digital / digital-to-analog converters and other precision analog circuitry).

The device version B (available on request) implements power good circuit (PG) which indicates that output voltage is in regulation. This signal could be used for power sequencing or as a microcontroller reset signal.

Internal short circuit and over temperature protections saves the device against overload conditions.

## Features

- Operating Input Voltage Range: 2.7 V to 38 V

- Output Voltage Adjustable Range: 1.2 V to 35 V

- Fixed Output Voltage Versions: 3.3 V and 5.0 V (other voltage versions on request)

- Very Low Noise: 10 μV<sub>RMS</sub> (10 Hz to 100 kHz)

- Low Quiescent Current: 50 µA typ.

- Low Shutdown Current: 100 nA typ.

- Low Dropout: 290 mV typ. at 150 mA

- Output Voltage Accuracy ±0.6% (25°C)

- Programmable Soft Start Circuit

- Power Good Output with Programmable Delay Time (device version B – available on request)

- Stable with Small 1 µF Ceramic Capacitors

- Over-Current and Thermal Shutdown Protections

- Available in Micro-8 EP Package

- Device is Pb-Free and RoHS Compliant

## **Typical Applications**

- Supply Rails for OpAmps, ADCs, DACs and other Precision Analog Circuitry and Audio

- Post DC–DC Converter Regulation and Ripple Filtering

- Test and Measurement

- Industrial Instrumentation

- Metering

- Battery Powered Devices

This document contains information on a product under development. ON Semiconductor reserves the right to change or discontinue this product without notice.

## **ON Semiconductor®**

www.onsemi.com

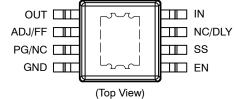

Micro8 EP CASE 846AT

## MARKING DIAGRAM

W ΖZ = Assembly Lot Code

А Υ

## **ORDERING INFORMATION**

See detailed ordering and shipping information on page 5 of this data sheet.

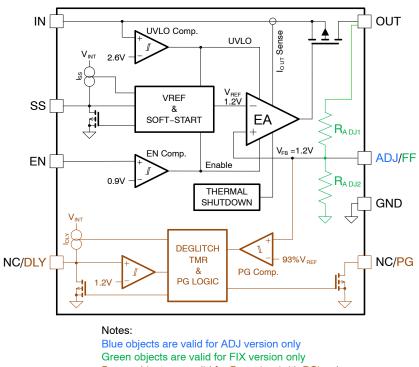

Brown objects are valid for B version (with PG) only

Black objects are common for all version

## **PIN DESCRIPTION**

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                                                                                              |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8          | IN       | Power supply input pin.                                                                                                                                                                                                                                                                                                                                  |

| 4          | GND      | Ground pin.                                                                                                                                                                                                                                                                                                                                              |

| 1          | OUT      | LDO output pin.                                                                                                                                                                                                                                                                                                                                          |

| 5          | EN       | Enable input pin (high = enable, low = disable). If this pin is not needed it should be conned to IN pin.<br>No internal pull-up or pull-down circuit is present.                                                                                                                                                                                        |

| 2          | ADJ/FF   | <ul> <li>ADJ version – pin is ADJ</li> <li>Adjust input pin. Could be connected directly or by the resistor divider to the output pin.</li> <li>FIX versions – pin is FF</li> <li>Feed forward capacitor pin. Could be connected by C<sub>FF</sub> capacitor to OUT pin for better dynamic performance &amp; lower noise or left unconnected.</li> </ul> |

| 3          | NC/PG    | <ul> <li>Device version A (without PG) – pin is NC</li> <li>Not internally connected. Could be left unconnected or connected to GND.</li> <li>Device version B (with PG) – pin is PG</li> <li>Power good output pin. High impedance for power ok, low level for fail. Could be left unconnected or connected to GND if not used.</li> </ul>              |

| 7          | NC/DLY   | <ul> <li>Device version A (without PG) – pin is NC</li> <li>Not internally connected. Could be left unconnected or connected to GND.</li> <li>Device version B (with PG) – pin is DLY</li> <li>Power good delay pin. Connect a C<sub>DLY</sub> capacitor to set delay time. Could be left floating if not used.</li> </ul>                               |

| 6          | SS       | Soft-start input pin. Connect a C <sub>SS</sub> capacitor to set soft-start time. Could be left floating if not used.                                                                                                                                                                                                                                    |

| EP         | EPAD     | Exposed pad, must be connected to GND.                                                                                                                                                                                                                                                                                                                   |

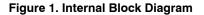

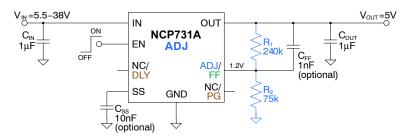

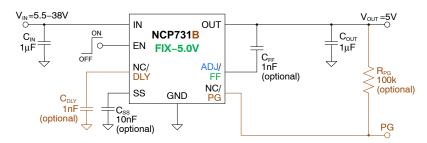

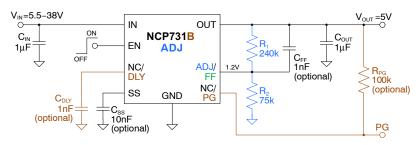

### **TYPICAL APPLICATION SCHEMATICS**

Figure 2. Fixed Output Voltage Application, 5 V, Device Version-A (without PG)

Figure 3. Adjustable Output Voltage Application, 5 V, Device Version-A (without PG)

Figure 4. Fixed Output Voltage Application, 5 V, Device Version-B (with PG)

Figure 5. Adjustable Output Voltage Application, 5 V, Device Version-B (with PG)

Notes: Blue objects are valid for ADJ version only Green objects are valid for FIX version only Brown objects are valid for B version (with PG) only Black objects are common for all version

#### **Table 1. MAXIMUM RATINGS**

| Rating                                        | Symbol              | Value                                                         | Unit |

|-----------------------------------------------|---------------------|---------------------------------------------------------------|------|

| IN Voltage (Note 1)                           | V <sub>IN</sub>     | -0.3 to 40                                                    | V    |

| OUT Voltage                                   | V <sub>OUT</sub>    | -0.3 to [(V <sub>IN</sub> + 0.3) or 40 V; whichever is lower] | V    |

| EN Voltage                                    | V <sub>EN</sub>     | –0.3 to (V <sub>IN</sub> + 0.3)                               | V    |

| ADJ/FF Voltage                                | V <sub>ADJ</sub>    | -0.3 to 5.5                                                   | V    |

| SS Voltage                                    | V <sub>SS</sub>     | -0.3 to 5.5                                                   | V    |

| PG Voltage                                    | V <sub>PG</sub>     | –0.3 to (V <sub>IN</sub> + 0.3)                               | V    |

| DLY Voltage                                   | V <sub>DLY</sub>    | -0.3 to 5.5                                                   | V    |

| Output Current                                | lout                | Internally limited                                            | mA   |

| PG Current                                    | I <sub>PG</sub>     | 3                                                             | mA   |

| Maximum Junction Temperature                  | T <sub>J(MAX)</sub> | 150                                                           | °C   |

| Storage Temperature                           | T <sub>STG</sub>    | –55 to 150                                                    | °C   |

| ESD Capability, Human Body Model (Note 2)     | ESD <sub>HBM</sub>  | 2000                                                          | V    |

| ESD Capability, Charged Device Model (Note 2) | ESD <sub>CDM</sub>  | 1000                                                          | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

2. This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per ANSI/ESDA/JEDEC JS-001, EIA/JESD22-A114 ESD Charged Device Model tested per ANSI/ESDA/JEDEC JS-002, EIA/JESD22-C101

#### Table 2. THERMAL CHARACTERISTICS (Note 3)

| Characteristic                                              | Symbol               | Value | Unit |

|-------------------------------------------------------------|----------------------|-------|------|

| Thermal Resistance, Junction-to-Air                         | $R_{\theta JA}$      | 47    | °C/W |

| Thermal Resistance, Junction-to-Case (top)                  | $R_{\theta JCt}$     | TBD   | °C/W |

| Thermal Resistance, Junction-to-Case (bottom)               | $R_{	ext{	heta}JCb}$ | TBD   | °C/W |

| Thermal Resistance, Junction-to-Board (top)                 | $R_{\theta JBt}$     | TBD   | °C/W |

| Thermal Characterization Parameter, Junction-to-Case (top)  | $\Psi_{JCt}$         | TBD   | °C/W |

| Thermal Characterization Parameter, Junction-to-Board [FEM] | $\Psi_{JB}$          | TBD   | °C/W |

3. Measured according to JEDEC board specification (board 1S2P, Cu layer thickness 1 oz, Cu area 650 mm<sup>2</sup>, no airflow). Detailed description of the board can be found in JESD51-7.

| Table 3. ELECTRICAL CHARACTERISTICS $V_{IN} = V_{OUT-NOM} + 1 V$ and $V_{IN} \ge 2.7 V$ , $V_{EN} = 1.2 V$ , $I_{OUT} = 1 mA$ , $C_{IN} = C_{OUT} = 1.0 \mu M$ | F |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| (Note 4), $C_{SS} = 0$ nF, $C_{FF} = 0$ nF, $T_J = -40^{\circ}$ C to 125°C, ADJ tied to OUT, unless otherwise specified.                                       |   |

| Parameter                 | Test Conditions                                                                                                                 | Symbol            | Min              | Тур  | Max | Unit |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|------|-----|------|

| Recommended Input Voltage |                                                                                                                                 | V <sub>IN</sub>   | 2.7              | -    | 38  | V    |

| Output Voltage Accuracy   | $T_J = +25^{\circ}C$                                                                                                            | V <sub>OUT</sub>  | -0.6             | -    | 0.6 | %    |

|                           | V <sub>IN</sub> = V <sub>OUT-NOM</sub> + 1 V to 38 V<br>I <sub>OUT</sub> = 0.1 mA to 150 mA<br>T <sub>J</sub> = -40°C to +125°C |                   | -1.5             | _    | 1.5 |      |

| Output Voltage Range      |                                                                                                                                 | V <sub>OUT</sub>  | V <sub>ADJ</sub> | -    | 35  | V    |

| ADJ Reference Voltage     |                                                                                                                                 | V <sub>ADJ</sub>  | -                | 1.2  | -   | V    |

| ADJ Input Current         | V <sub>ADJ</sub> = 1.2 V                                                                                                        | I <sub>ADJ</sub>  | -0.1             | 0.01 | 0.1 | μΑ   |

| Quiescent Current         | $V_{IN} = V_{OUT-NOM} + 1 V \text{ to } 38 V, I_{OUT} = 0 \text{ mA}$                                                           | Ι <sub>Q</sub>    | -                | 48   | 100 | μΑ   |

| Ground Current            | I <sub>OUT</sub> = 150 mA                                                                                                       | I <sub>GND</sub>  | -                | 500  | -   | μΑ   |

| Shutdown Current          | V <sub>EN</sub> = 0 V, V <sub>IN</sub> = 38 V                                                                                   | I <sub>SHDN</sub> | -                | 0.2  | 1.5 | μA   |

| Output Current Limit      | V <sub>OUT</sub> = V <sub>OUT-NOM</sub> – 100 mV                                                                                | I <sub>OLIM</sub> | 210              | 280  | 450 | mA   |

| Short Circuit Current     | V <sub>OUT</sub> = 0 V                                                                                                          | I <sub>OSC</sub>  | 210              | 280  | 450 | mA   |

| Table 3. ELECTRICAL CHARACTERISTICS $V_{IN} = V_{OUT-NOM} + 1 V$ and $V_{IN} \ge 2.7 V$ , $V_{EN} = 1.2 V$ , $I_{OUT} = 1 mA$ , $C_{IN} = C_{OUT} = 1.0 \mu F$ |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| (Note 4), $C_{SS} = 0$ nF, $C_{FF} = 0$ nF, $T_J = -40^{\circ}C$ to 125°C, ADJ tied to OUT, unless otherwise specified.                                        |  |

| Parameter                            | Test Conditions                                                                                    |                  | Symbol                 | Min  | Тур  | Max  | Unit  |

|--------------------------------------|----------------------------------------------------------------------------------------------------|------------------|------------------------|------|------|------|-------|

| Dropout Voltage (Note 5)             | I <sub>OUT</sub> = 150 mA                                                                          |                  | V <sub>DO</sub>        | -    | 290  | 480  | mV    |

| Power Supply Ripple Rejection        | V <sub>IN</sub> = V <sub>OUT-NOM</sub> + 2 V                                                       | 10 Hz            | PSRR                   | _    | 80   | -    | dB    |

|                                      | I <sub>OUT</sub> = 10 mA                                                                           | 10 kHz           |                        | -    | 70   | -    |       |

|                                      |                                                                                                    | 100 kHz          |                        | -    | 42   | -    | -     |

|                                      |                                                                                                    | 1 MHz            |                        | -    | 48   | -    |       |

| Output Noise Voltage                 | f = 10 Hz to 100 kHz, ADJ version,<br>V <sub>OUT</sub> = V <sub>ADJ</sub> , C <sub>FF</sub> = 1 nF |                  | V <sub>N</sub>         | -    | 10   | -    | μVRMS |

|                                      | f = 10 Hz to 100 kHz, FIX version,<br>V <sub>OUT</sub> = 5 V, C <sub>FF</sub> = 1 nF               |                  |                        | -    | TBD  | -    |       |

| EN Threshold                         | V <sub>EN</sub> rising                                                                             |                  | V <sub>EN-TH</sub>     | 0.7  | 0.9  | 1.1  | V     |

| EN Hysteresis                        | V <sub>EN</sub> falling                                                                            |                  | V <sub>EN-HY</sub>     | 0.02 | 0.1  | 0.2  | V     |

| EN Input Current                     | V <sub>EN</sub> = 30 V, V <sub>IN</sub> = 30 V                                                     |                  | I <sub>EN</sub>        | -1   | 0.05 | 1    | μA    |

| Internal UVLO Threshold              | V <sub>IN</sub> voltage rising                                                                     |                  | V <sub>UVLO-TH</sub>   | 2.51 | 2.6  | 2.69 | V     |

| Internal UVLO Hysteresis             | V <sub>IN</sub> voltage falling                                                                    |                  | V <sub>UVLO-HY</sub>   | 0.01 | 0.05 | 0.09 | V     |

| SS Charging Current                  | V <sub>SS</sub> = 0 V                                                                              |                  | I <sub>SS</sub>        | 765  | 850  | 935  | nA    |

| SS High Voltage                      | SS pin floating                                                                                    |                  | V <sub>SS-HI</sub>     | -    | 2.4  | -    | V     |

| SS Time (Note 6)                     | C <sub>SS</sub> = 10 nF                                                                            |                  | t <sub>SS-10n</sub> F  | -    | 14   | -    | ms    |

|                                      | C <sub>SS</sub> not connected                                                                      |                  | t <sub>SS-0nF</sub>    | -    | TBD  | -    | μs    |

| DLY Charging Current (Note 7)        | V <sub>DLY</sub> = 0 V                                                                             |                  | I <sub>DLY</sub>       | -    | 1.2  | -    | μA    |

| DLY High Voltage (Note 7)            | DLY pin floating                                                                                   | DLY pin floating |                        | -    | 2.4  | -    | V     |

| DLY Threshold Voltage (Note 7)       | DLY voltage rising                                                                                 |                  | V <sub>SS-TH</sub>     | 1.1  | 1.2  | 1.3  | V     |

| DLY Hysteresis (Note 7)              | DLY voltage falling                                                                                |                  | V <sub>SS-HY</sub>     | 0.05 | 0.1  | 0.15 | V     |

| DLY Time (Note 7)                    | C <sub>DLY</sub> = 10 nF                                                                           |                  | t <sub>DLY-10n</sub> F | 8    | 10   | 12   | ms    |

|                                      | C <sub>DLY</sub> not connected                                                                     |                  | t <sub>DLY-0n</sub> F  |      | TBD  |      | μs    |

| PG Threshold (Note 7)                | V <sub>OUT</sub> falling                                                                           |                  | V <sub>PG-TH</sub>     | 90   | 93   | 96   | %     |

| PG Hysteresis (Note 7)               | V <sub>OUT</sub> rising                                                                            |                  | V <sub>PG-HY</sub>     | 0.5  | 2    | 3.5  | %     |

| PG Deglitch Time (Note 7)            |                                                                                                    |                  | t <sub>PG-DG</sub>     | 100  | 200  | 300  | μs    |

| PG Output Low Level Voltage (Note 7) | I <sub>PG</sub> = 1 mA                                                                             |                  | V <sub>PG-LO</sub>     | -    | 0.2  | 0.4  | V     |

| PG Output Leakage Current (Note 7)   | V <sub>PG</sub> = 30 V                                                                             |                  | I <sub>PG-LK</sub>     | _    | 0.01 | 1    | μA    |

| Thermal Shutdown Temperature         | Temperature rising from $T_J = +25^{\circ}C$                                                       |                  | T <sub>TSD</sub>       | _    | 170  | -    | °C    |

| Thermal Shutdown Hysteresis          | Temperature falling from TSD                                                                       |                  | T <sub>TSDH</sub>      | _    | 10   | -    | °C    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

4. Effective capacitance, including the effect of DC bias, tolerance and temperature. See the Application Information section for more information.

5. Dropout measured when the output voltage falls 100 mV below the nominal output voltage. Limits are valid for all voltage versions.

Startup time is the time from EN assertion to point when output voltage is equal to 95% of V<sub>OUT-NOM</sub>.

Applicable only to device version B (option with power good output). PG threshold and PG hysteresis are expressed in percentage of nominal output voltage.

#### **ORDERING INFORMATION**

| Part Number     | Marking | Voltage Option (V <sub>OUT-NOM</sub> ) | Version       | Package                               | Shipping |  |

|-----------------|---------|----------------------------------------|---------------|---------------------------------------|----------|--|

| NCP731ADN330R2G | 731A33  | 3.3 V                                  |               |                                       |          |  |

| NCP731ADN500R2G | 731A50  | 5.0 V                                  | Without<br>PG | Micro–8 EP<br>(Pb–Free)               | TBD      |  |

| NCP731ADNADJR2G | 731AAD  | ADJ                                    |               | , , , , , , , , , , , , , , , , , , , |          |  |

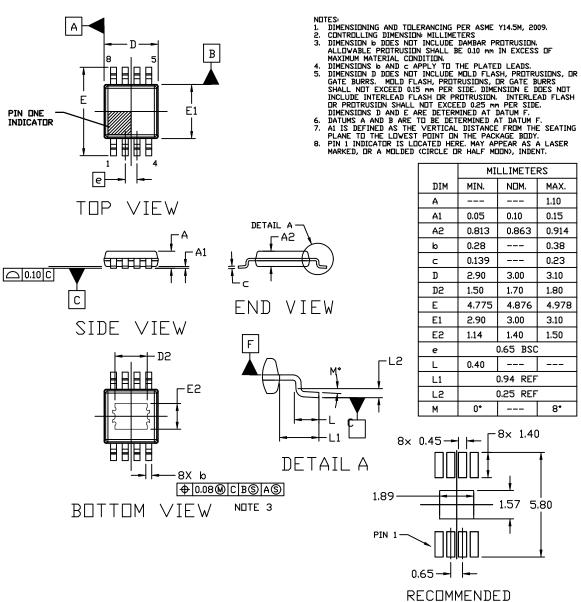

#### PACKAGE DIMENSIONS

## MSOP8 EP 3x3

CASE 846AT ISSUE O

## MOUNTING FOOTPRINT

For additional information on our Pb-Free strategy and soldering details, please download the DN Semiconductor Soldering and Mounting Techniques Reference Manual, SDLDERRM/D.

coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney des arising out of, directly or indirectly any claim of personal injury or death associated with such unintended or unauthorized use, guers is used claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

#### TECHNICAL SUPPORT

ON Semiconductor Website: www.onsemi.com

North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative

ON Semiconductor and ware trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent literature is subject to all applicable copyright laws and is not for resale in any manner.